The part about history

The ability to track and display the scores on the screen was a big selling point for any consoles made with the chip (and thus the chip itself.) Prior to it's release, digital scoring was difficult to implement from a price/complexity standpoint. Arcade machines have a bigger component budget than home consoles, so they generated their on-screen scores with a handful of standard logic chips (e.g. 7400-series or CMOS equivalent), which made up a board containing dozens of chips. Early home consoles could only contain small numbers of chips or discrete transistors (the Magnavox Odyssey had 37 transistors and no ICs) to be competitively priced, so they didn't include features such as digital ball motion, multiple paddles, play-fields, and of course on-screen scoring. Many consoles instead had plastic sliders on them to keep track of scores, or had a simpler circuit in which every scored point moved a square across the screen.

|

| The inside of the VideoSport MK II, showing standard discrete system innards (photo: Andy Lewis) |

Very few systems, such as URL's VA2 systems had these features, because they contained a real arcade circuit board re-purposed for home use. Most people probably did not want to pay 500$ for one of these systems though (2018 price: ~$2,300 or ~1765₤ or ~1979€ aka "very expensive" according to online calculators.) Electronics simply cost too much to allow home systems to play anything more than primitive analog Pong.

Technology was steadily improving however, by 1975 it was possible to fit thousands of transistors onto a single chip. Atari was the first to create and use a custom chip, allowing their systems to have on-screen scoring, color, sound, and digital ball motion at a very competitive price. They kept the chip to themselves though, giving them an edge over other home systems. General Instruments, a big semiconductor company, knew that the many companies that cloned the arcade PONG would want to follow Atari to the home market, so they designed a capable PONG (clone) and sold it to anyone. Thus the AY-3-8500 was born.

|

| Circuit board of the Binatone TV master, a standard AY-3-8500 based system. The circuit board is sparsely populated, yet it has many more features then the system above. (From Dave Curran's blog post) |

The score registers

The scores are stored in two 4-bit ripple counters, allowing scores from 0-15. Those with a good eye may have spotted them on the right side of the chip. Confusingly, the left counter holds the right player's score and vice-versa. I'm referring to these as "registers" even though they are not software-accessible CPU registers (the chip is in no way a microprocessor.)

|

| The two score "ripple" counters |

This "ripple counter" isn't built like a standard ripple counter. In a normal ripple counter, each unit is made of a JK flip-flop connected to it's neighbors which serves as a divide/2 circuit. Each pulse will make the counter advance in binary order. This strange circuit also counts in binary order, it's wired a bit differently however. First, each unit is a little more complex, with multiple SR latches in them. This may make them behave more like JK Master-Slave flip flops (JK-MS flip flops exist where race conditions may be a threat to logic integrity.) Second, the increment signal is connected to every unit, and serves to disable their advance by grounding their carry signals. Because of this, only the top (LSB) counter will advance when the increment single is turned on, when it turns off the next bit is allowed to advance.

This pattern continues down the chain: Each unit is prevented from carrying unless all the units above (less significant) are in a "1" state. You can see this in the picture to the left, the vertical wires in the middle are the increment and output wires (A "1" = grounded) which are each connected through a green transistor to the lower (more significant) bits.

These 8 bits continue on to the decoding circuity. One last note, the registers will roll over to zero once a 1 is added to 15. A NOR gate below the registers will activate when all bits hold 1s, this prevents the score from "increasing" any farther, locking it at 15.

Decoding

|

| The multiplexer |

The 8 output wires from the score counters travel to the left in a "U" shape. These connections end in a multiplexer which selects which player's score is fed into the decoder. The multiplexer is a set of 8 NAND gates, four are powered by either the drawLeftScore or drawRightScore at any one time. The NAND gates are very simple, instead of a transistor with one side connected to ground, its side is connected to another transistor with it's other side connected to ground. Both transistors must be on to ground the output, making a NAND gate.

Following drawLeftScore leads to a flip flop controlled by horizontal control lines 6 & 12 (these are triggered at the center and left walls respectively.) The drawRightScore node is the opposite state of this. If you run the simulation, you should be able to see that the value going into the decoding circuitry will be switched to the other player's score at these points.

Above the multiplexer is a binary decoder (see below). One 4-bit value goes in, one of the 16 (24) output lines is activated (this is called one-hot as only one is active at a time.) To accomplish this the 4-bit value is inverted to make a total of 8 inputs, these much match up with the transistors to allow the output to be pulled high. At the top of the decoder are three transistors connected to the most, second most, and third most significant inputs. These transistors build a (bit3 AND (bit1 OR bit2)) gate. Numerically, this functions as a >9 check for 4-bit numbers, indicating if the circuitry should draw a "1" in front of the digit. We'll see where this "draw 1" signal leads to in a moment.

|

| First part of the decoding circuitry. The decoder (right) turns a 4-bit number into one of 16 outputs (light blue) These can trigger one of 10 inputs (yellow) into the encoder (left) |

Some of the 16 possible outputs are ORed into 10 output lines as they travel to the left (with a NOT+NOR circuit) as the circuitry only needs to know the other digit. 13 and 3 are ORed onto the "3" signal, 12 and 2 onto the "2" etc. 6 is not ORed as there is no output 16. These 10 signals go into an encoder (left) indicating which 10 segments of the digit should be drawn.

Parts of the digits

|

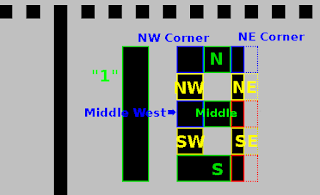

| The different segments of the score, and their names. |

One thing that made me scratch my head for a while is the fact that the scores are not symmetrical, the rightmost side looks cut-off. This wasn't due to a bug by me as I found out, but by the chip's design. Looking closely at some footage (skip to 4:13 and look at the "11"s) I found that this exists in real chips, at least some revision of them.

Circuitry to track the current row being drawn is above the encoder to the left. The HsyncNOT_ON2 signal, which is toggled once per scanline, goes into a 2-segment shift register which functions as a one-quarter signal divider. Each scanline * 4 * 2 (due to interlacing) = 8 scanlines, thus each row is 8

scanlines high. This divided signal advances the 3-bit linear feedback shift register (LFSR) on the right, which keeps track of the raster beam's vertical position. This counter is normally kept at 0 unless the currently drawn spot is between vertical signal 7 (below sideline) and 8 (below score) due to a latch. This latch also directly disables the score output.

The 3 pairs of signals from the LFSR counter travel into a decoder where they activate from top to bottom (on the chip), the Top, Bottom, Middle, Upper, Lower, and Disable row signals (see picture). These five signals travel rightward into a matrix of specialized logic which compare them with the ten possible score-based signals to generate the right side, middle, and left side of the digit.

This logic matrix is above, note that the right, middle, and left signals are active low. You can see how the constant segments are implemented, the two red transistors (connected to Vcc) force the upper and lower middle segments off, creating the holes in the digit "8" and every other digit. The right-side bottom and middle segments are grounded by the blue transistors and thus always on. The wide transistor t the left of the "Bottom" label controls both the left and middle segments, making the "South" signal affect both. Smart tricks like these reduce the number of transistors and die space needed to implement the circuitry, as both were at a premium in the mid-1970s.

The last component in this chain of score circuitry converts the four segment draw signals (right, middle, left, and "1") into a single, timed signal. The chip uses a shift register to do this. Unlike the previous shift registers, this one takes in a parallel input and shifts it out serially. This shift register is located directly below the encoder and the encoder's inputs. Also unlike the previous shift registers, this one does not have an orderly repeating structure. Another interesting thing about it is that there are some "missing" transistors, spots where they look like they should be but aren't. It's possible that the designers changed the circuit after drawing part of it, and didn't remove the old traces from the layout.

The last component in this chain of score circuitry converts the four segment draw signals (right, middle, left, and "1") into a single, timed signal. The chip uses a shift register to do this. Unlike the previous shift registers, this one takes in a parallel input and shifts it out serially. This shift register is located directly below the encoder and the encoder's inputs. Also unlike the previous shift registers, this one does not have an orderly repeating structure. Another interesting thing about it is that there are some "missing" transistors, spots where they look like they should be but aren't. It's possible that the designers changed the circuit after drawing part of it, and didn't remove the old traces from the layout.

The shifter's operation is fairly straightforward, 10 wires with no pullup transistors function as capacitors. A load signal called at the left side of each score fills every other capacitor with the four possible values, plus one which is always low to create a gap between the 1 and the digit on the screen. The two clock signals alternate on and off during the width of the score at half the normal clock rate, first green on red off, then red on green off. Each toggle of the clock will cause half of the capacitors to override the capacitor to the right (with an inverted value). The bits travel from left to right so the "1" signal is output first, and the digit's right side last.

These bits control a large transistor (in the lower right in the screenshot above) which drives a wire leading towards the lower-left corner of the chip. Two other signals may disable the score output wire, the latch from the vertical circuitry, and a circuit that serves to hide the scores during some parts of the rifle games. The score output intersects with the field generation circuitry and goes to the score/field output pin. Outside the chip it is mixed with the other outputs and possibly given color, creating a viewable television signal. ...And thus, as advertised, digital on-screen scoring! (the '70s were a whole different time...)

And that's all folks! I'm glad I managed to get in a last-minute post before the RetroChallenge ended. I'm wondering how many others had 11th hour sprints... Looking ahead I've got some ideas for both a small and large project which I'll describe in a little more detail soon. For now, thanks for reading, and I hope you all had a wonderful September!

| Vertical score position tracking |

scanlines high. This divided signal advances the 3-bit linear feedback shift register (LFSR) on the right, which keeps track of the raster beam's vertical position. This counter is normally kept at 0 unless the currently drawn spot is between vertical signal 7 (below sideline) and 8 (below score) due to a latch. This latch also directly disables the score output.

The 3 pairs of signals from the LFSR counter travel into a decoder where they activate from top to bottom (on the chip), the Top, Bottom, Middle, Upper, Lower, and Disable row signals (see picture). These five signals travel rightward into a matrix of specialized logic which compare them with the ten possible score-based signals to generate the right side, middle, and left side of the digit.

|

| The logic matrix. The disable signal is present when none of the other vertical signals are. |

This logic matrix is above, note that the right, middle, and left signals are active low. You can see how the constant segments are implemented, the two red transistors (connected to Vcc) force the upper and lower middle segments off, creating the holes in the digit "8" and every other digit. The right-side bottom and middle segments are grounded by the blue transistors and thus always on. The wide transistor t the left of the "Bottom" label controls both the left and middle segments, making the "South" signal affect both. Smart tricks like these reduce the number of transistors and die space needed to implement the circuitry, as both were at a premium in the mid-1970s.

The shift register

The last component in this chain of score circuitry converts the four segment draw signals (right, middle, left, and "1") into a single, timed signal. The chip uses a shift register to do this. Unlike the previous shift registers, this one takes in a parallel input and shifts it out serially. This shift register is located directly below the encoder and the encoder's inputs. Also unlike the previous shift registers, this one does not have an orderly repeating structure. Another interesting thing about it is that there are some "missing" transistors, spots where they look like they should be but aren't. It's possible that the designers changed the circuit after drawing part of it, and didn't remove the old traces from the layout.

The last component in this chain of score circuitry converts the four segment draw signals (right, middle, left, and "1") into a single, timed signal. The chip uses a shift register to do this. Unlike the previous shift registers, this one takes in a parallel input and shifts it out serially. This shift register is located directly below the encoder and the encoder's inputs. Also unlike the previous shift registers, this one does not have an orderly repeating structure. Another interesting thing about it is that there are some "missing" transistors, spots where they look like they should be but aren't. It's possible that the designers changed the circuit after drawing part of it, and didn't remove the old traces from the layout. |

| A diagram for the score shift register |

These bits control a large transistor (in the lower right in the screenshot above) which drives a wire leading towards the lower-left corner of the chip. Two other signals may disable the score output wire, the latch from the vertical circuitry, and a circuit that serves to hide the scores during some parts of the rifle games. The score output intersects with the field generation circuitry and goes to the score/field output pin. Outside the chip it is mixed with the other outputs and possibly given color, creating a viewable television signal. ...And thus, as advertised, digital on-screen scoring! (the '70s were a whole different time...)

And that's all folks! I'm glad I managed to get in a last-minute post before the RetroChallenge ended. I'm wondering how many others had 11th hour sprints... Looking ahead I've got some ideas for both a small and large project which I'll describe in a little more detail soon. For now, thanks for reading, and I hope you all had a wonderful September!